台积电2nm N2工艺节点今年投产 A16和N2P明年上市

台积电在其 2025 年北美技术研讨会上透露,该公司有望在今年下半年开始大批量生产 N2(2nm 级)芯片,这是其首个依赖于全环绕栅极 (GAA) 纳米片晶体管的生产技术。

这个新节点将支持明年推出的众多产品,包括 AMD 用于数据中心的下一代 EPYC“Venice”CPU,以及各种面向客户端的处理器,例如用于智能手机、平板电脑和个人电脑的 Apple 2025 芯片。得益于 GAAFET 和增强的功率传输,新的 2nm 节点将在更高的性能和晶体管密度中实现切实的节能。此外,后续工艺技术 A16 和 N2P 有望于明年投产。

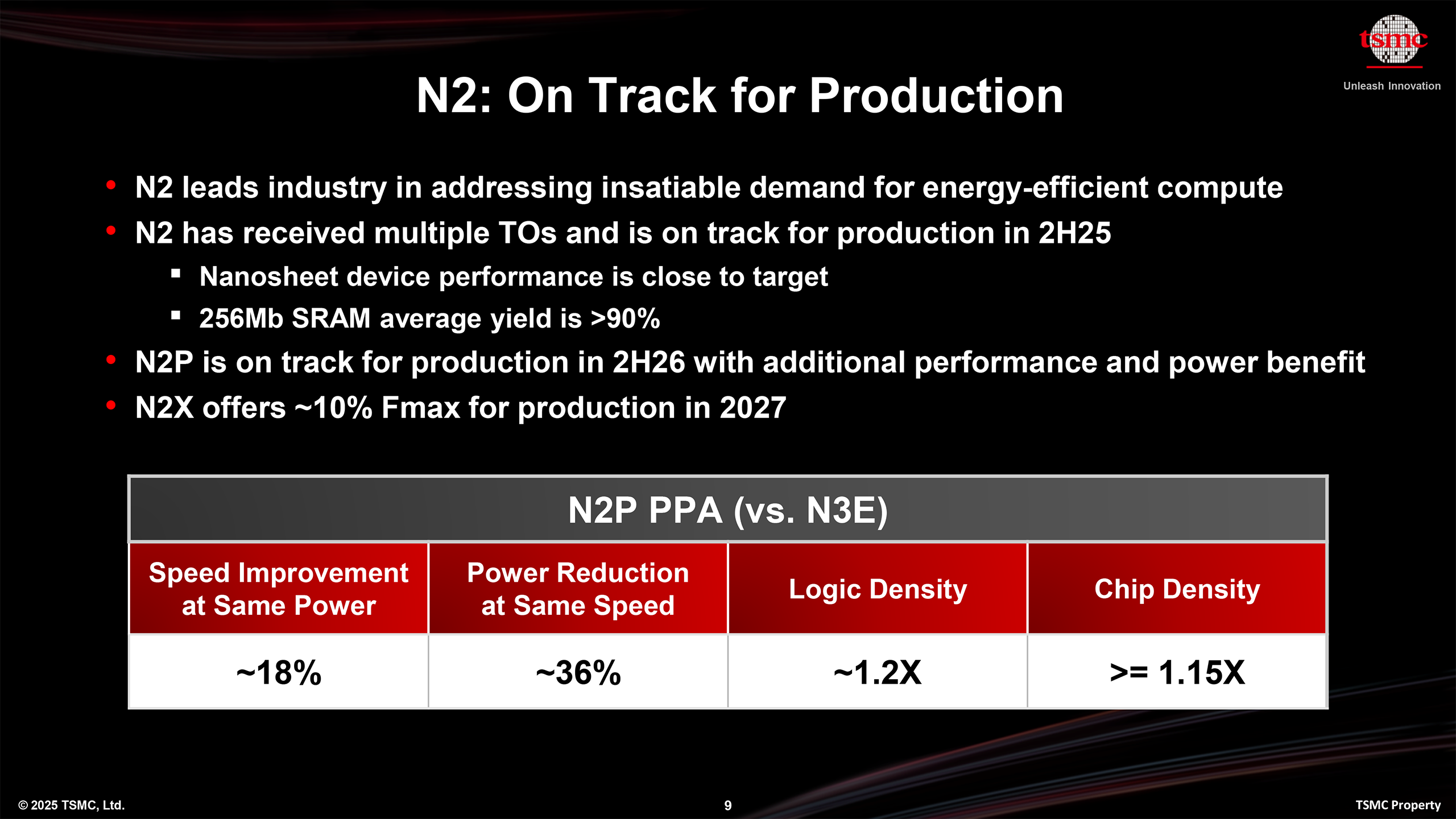

N2:准备在 2025 年下半年量产

N2 是该公司的全新工艺技术,将实现台积电所谓的“全节点改进”,其中包括与 N3E 相比,性能提高 10% 至 15%,功耗降低 25% 至 30%,晶体管密度增加 15%。台积电表示,N2 的晶体管性能接近目标,256Mb SRAM 模块的平均良率超过 90%,这表明随着 N2 走向量产,工艺成熟度很高。

(图片来源:台积电)

如上所述,N2 将是台积电第一个使用 GAA 纳米片晶体管的节点,当栅极 360 度环绕通道时,该晶体管有望提高性能并降低泄漏——在 N2 的情况下,通道的形状为多个水平纳米片。这种结构允许最大限度地对通道进行静电控制,从而在不影响性能或功率的情况下最小化晶体管尺寸,从而实现更高的晶体管密度。

此外,N2 工艺将超高性能金属绝缘体金属 (SHPMIM) 电容器集成到晶体管的输电电路中,以增强电源稳定性和性能。与该公司之前的超高密度金属-绝缘体-金属 (SHDMIM) 设计相比,这些新型电容器的电容密度增加了一倍以上,并且与上一代产品相比,薄层电阻 (Rs) 和通孔电阻 (Rc) 降低了 50%,这应该会对性能和功耗产生切实影响。

宣传 TSMC 新工艺技术的 PPA 改进

| Tom 的硬件 | N2 与 N3E | N2P 与 N3E | N2P 与 N2 | A16 与 N2P | N2X 与 N2P |

| 权力 | -25% ~ -30% | -36% | -5% ~ -10% | -15% ~ -20% | 降低 |

| 性能 | 10% - 15% | 18% | 5% - 10% | 8% - 10% | 10% |

| 密度* | 1.15 倍 | 1.15 倍 | ? | 1.07 倍 - 1.10 倍 | ? |

| 晶体管 | GAA | GAA | GAA | GAA | GAA |

| 电力输送 | 正面带 SHPMIM | 正面带 SHPMIM | 正面带 SHPMIM | 战略风险 | 正面带 SHPMIM (?) |

| HVM 系列 | 2025 年下半年 | 2026 年下半年 | 2026 年下半年 | 2026 年下半年 | 2027 |

*TSMC 公布的芯片密度反映了由 50% 逻辑、30% SRAM 和 20% 模拟组成的“混合”芯片密度。

**在同一区域。

以相同的速度。

该制造工艺有望在今年下半年进入量产,并将在明年推出众多产品,包括 AMD 用于数据中心的下一代 EPYC“Venice”CPU,以及各种面向客户端的处理器,例如用于智能手机、平板电脑和个人电脑的 Apple 2025 片上系统。